Itgalpur, Rajankunte, Yelahanka, Bengaluru – 560064

| Course Code:               | Course Title: ADVANCED DI<br>DESIGN                                  | GITAL SYSTEM       | L- P- C              | 3          | 0              | 3                          |

|----------------------------|----------------------------------------------------------------------|--------------------|----------------------|------------|----------------|----------------------------|

| ECE5005                    |                                                                      | ogram Core)        |                      | 5          | Ũ              | 5                          |

| Version No.                | 1.0                                                                  |                    |                      |            | I              |                            |

| Course Pre-requisites      | Basic concepts of digital ci                                         | rcuits like gates  | , flip-flop          | s, regis   | ters, m        | ultiplexers,               |

|                            | decoders etc.                                                        |                    |                      |            |                |                            |

| Anti-requisites            | NIL                                                                  |                    |                      |            |                |                            |

| Course Description         | The focus of this course is                                          | to enable the stud | lents to D           | esign th   | e synch        | ronous and                 |

|                            | Asynchronous Digital Sys                                             | tems through th    | e study              | of ASN     | 1 & FS         | SM charts,                 |

|                            | Hardware description languation                                      | age coding, Redu   | ction and            | assignm    | ents of s      | tate tables.               |

|                            | Further, it elaborates the Te                                        | est Generation an  | d Fault d            | iagnosis   | s of Con       | nbinational                |

|                            | circuits by conventional n                                           | nethods. It intro  | duces va             | rious m    | ethods         | to analyze                 |

|                            | sequential circuits. Further                                         |                    |                      |            |                | 2                          |

|                            | devices. This course emphas                                          |                    |                      | •          |                | -                          |

|                            | electronic circuits.                                                 | izes i aut deteeti | und und              | .5110313 ( | , i i i u v di | ieea argitar               |

|                            | electronic circuits.                                                 |                    |                      |            |                |                            |

| Course Objective           | The objective of the course                                          |                    |                      |            |                |                            |

|                            | ADVANCED DIGITAL SYSTEM<br>PARTICPATIVE LEARNIN                      |                    | tain <u>SKII</u>     | L DEVE     | LOPME          | <b>NT</b> through          |

|                            | FARING ALLY E LEARNIN                                                | NG .               |                      |            |                |                            |

| Course Outcomes            | On successful completion of t                                        | he course the stu  | idents sha           | ll be ab   | le to:         |                            |

|                            | CO1: Summarize th                                                    | e minimization tl  | heories of           | Sequer     | itial Mac      | chines.                    |

|                            | CO2: Discover the s                                                  | sequential circuit | using pro            | gramma     | able dev       | ices.                      |

|                            | CO3: Practice the t                                                  | echniques for fau  | ılt modeli           | ng of dig  | gital syst     | ems.                       |

|                            | CO4: Illustrate the                                                  | various Fault diag | gnosis algo          | orithm     |                |                            |

| Course Content:            |                                                                      |                    |                      |            |                |                            |

|                            | Minimization and                                                     |                    |                      | Decall     |                |                            |

| Module 1                   | Transformation of                                                    | Assignment         | Memory<br>based Qu   |            | 10             | Sessions                   |

|                            | Sequential Machines:                                                 |                    | -                    |            |                |                            |

|                            | Capabilities and limitations of F<br>tely specified machines. Fundar |                    |                      |            |                |                            |

| Minimal closed covers – Ra |                                                                      |                    |                      |            |                |                            |

| Module 2                   | Advanced Digital Design                                              | Assignment/        | Memory               | Recall     | 10             | Sessions                   |

|                            | and SM Charts:                                                       | mini project       | based Qu             |            |                |                            |

|                            | , PALs and PLAs, BCD Adder, 32 ider State machine charts,            |                    |                      |            |                |                            |

| Implementation of Binary   |                                                                      | Derivation of Si   | vi Cildits,          | NedilZd    |                | Sivi Clidit,               |

| <u>p.eeee</u>              |                                                                      | Assignment/        | Dueseus              |            |                |                            |

| Module 3                   | Fault Modeling                                                       | mini project       | Program simulation   | •          | 11             | Sessions                   |

|                            | latation & Daduadars - Early                                         |                    |                      |            |                |                            |

| -                          | letection & Redundancy Fault e<br>– Multiple stuck at fault model    | •                  |                      | оп –ғай    | it domin       |                            |

| <u> </u>                   |                                                                      | Assignment/        | 0                    | ing /      |                |                            |

| Module 4                   | Fault diagnosis                                                      | mini project       | Program<br>simulatic |            | 11             | Sessions                   |

|                            |                                                                      | RE                 | GISTRAR              | Registrar  | ) F            | Page <b>1</b> of <b>13</b> |

Fault diagnosis of combinational circuits by conventional methods – Path sensitization techniques, Test algorithms – D algorithm, PODEM, Random testing, Transition count testing, Signature analysis and test bridging faults.

#### Targeted Application & Tools that can be used:

This course is contributed for placement in data science companies, research & development work and also useful to know the existing & developing Artificial Intelligence.

# Professionally Used Software: HDL (VHDL/ Verilog HDL)/ C++ / MatLab, Phython

#### **Text Books:**

- 1. N. N. Biswas, *"Logic Design Theory"*, PHI, 2009. ISBN:9780135243985, 013524398X the University of Michigan- Prentice Hall

- 2. Zvi Kohavi, "Switching and Finite Automata Theory", TMH, 2nd Edition, 2005.

- 3. Norman Balabanian, Bradley Carlson, "Digital Logic Design Principles" Wiley Student Edition, 2007.

#### **Reference Books**

- 1. M. Abramovici, Melnin Breuer, Arthur Friedman, "Digital System Testing and Testable Design", Jaico Publications, Reprint Edition, 2008.

- 2. Charles H. Roth Jr., "Fundamentals of Logic Design", Cengage learning, 6th Edition, 2004.

- 3. Frederick. J. Hill & Peterson, "Computer Aided Logic Design", Wiley 4th Edition, 1993.

# **Online Resources (e-books, notes, ppts, video lectures etc)**

- 1. State Minimization in synchronous sequential circuits YouTube

- 2. Sequence detector 1100 || sequence detector 1101 overlapping mealy FSM YouTube

- 3. Ebook1: Find PDF Logic Design Theory (colorado.edu)

- 4. Ebook2: Digital Systems Design | Download book (freebookcentre.net)

- 5. Nptel Digital System Design Course (nptel.ac.in)

- 6. NPTEL :: Electrical Engineering NOC:Digital System Design

- 7. <u>https://www.researchgate.net/publication/348235247\_Advanced\_Digital\_System\_Design\_-</u> <u>A Practical Guide to Verilog Based FPGA and ASIC\_Implementation/link/5ff4764d92851c 13feefa0d2/download</u>

- 8. <u>https://www.researchgate.net/publication/3897013 Fault Equivalence Identification Using Red</u> <u>undancy Information and Static and Dynamic Extraction</u>

- 9. http://www.pld.ttu.ee/diagnostika/theory/fault.html

# Topics relevant to "Skill development": Machine Minimization

For developing **Skill development**" through **Participative Learning techniques**. This is attained through assessment component mentioned in course handout.

| Catalogue prepared by                       | Dr. G MUTHUPANDI                                 |

|---------------------------------------------|--------------------------------------------------|

| Recommended by the<br>Board of Studies on   | BOS NO: 15th BOS held on 28/07/2022              |

| Date of Approval by the<br>Academic Council | Academic Council Meeting No. 18, Dated 3/08/2022 |

anne REGISTRAR

idency University Act, 2013 of the Karnataka Act No. 41 of 2013 | Established under Section 2(f) of UGC Act, 19 Approved by AICTE, New Delhi

# A-2 [2022] COURSE HAND OUT

| SCHOOL                  | : SOE                                      |

|-------------------------|--------------------------------------------|

| DEPT.                   | : ECE                                      |

| DATE OF ISSUE           | : 27/08/2022                               |

| NAME OF THE PROGRAM     | : M. Tech                                  |

| P.R.C. APPROVAL REF.    | : PU/AC-18.4/ECE15/ESV/2022-24             |

| SEMESTER/YEAR           | :1                                         |

| COURSE TITLE & CODE     | : ADVANCED DIGITAL SYSTEM DESIGN & ECE5005 |

| COURSE CREDIT STRUCTURE | : 3-0-3                                    |

| CONTACT HOURS           | : 45                                       |

| COURSE INSTRUCTORS      | : Dr. Muthupandi G                         |

#### **PROGRAM OUTCOMES:**

REACH GREATER HEIGHTS

Graduates of the M. Tech. Program in Electronics and Communication Engineering will be able to:

PO1: An ability to analyze, manage and supervise engineering systems and processes with the aid of appropriate advanced tools.

PO2: An ability to design a system and process within constraints of health, safety, security, economics, manufacturability to meet desired needs.

PO3: An ability to carry out research in the respective discipline and publish the findings.

PO4: An ability to effectively communicate and transfer the knowledge/ skill to stakeholders.

PO5: An ability to realize the impact of engineering solutions in a contemporary, global, economical, environmental, and societal context for sustainable development.

#### **COURSE PREREQUISITES:**

Knowledge of C or Python Language, Knowledge of stm32 etc.,

**COURSE DESCRIPTION:**

The focus of this course is to enable the students to Design the synchronous and Asynchronous Digital Systems through the study of ASM & FSM charts, Hardware description language coding, Reduction and assignments of state tables. Further, it elaborates the Test Generation and Fault diagnosis of Combinational circuits by conventional methods. It introduces various methods to analyze sequential circuits. Further it elaborated the circuit design using programmable devices. This course emphasizes Fault detection and diagnosis of Advanced digital electronic circuits..

# **COURSE OBJECTIVES:**

The objective of the course is to familiarize the learners with the concepts of ADVANCED DIGITAL SYSTEM DESIGN and attain SKILL DEVELOPMENT through PARTICPATIVE LEARNING

# **COURSE OUTCOMES:**

On successful completion of the course the students shall be able to:

CO1: Summarize the minimization theories of Sequential Machines

CO2: Discover the sequential circuit using programmable devices.

CO3: Practice the techniques for fault modeling of digital systems.

CO4: Illustrate the various Fault diagnosis algorithm

# MAPPING OF C.O. WITH P.O.

[H-HIGH, M- MODERATE, L-LOW]

| CO N0. | PO 1 | PO 2 | PO 3 | PO 4 | PO 5 |

|--------|------|------|------|------|------|

| 1      | Н    | Н    | М    | L    | М    |

| 2      | L    | Н    | Н    | L    | М    |

| 3      | L    | Н    | М    | L    | М    |

| 4      | L    | М    | Н    | М    | Н    |

# **COURSE CONTENT (SYLLABUS):**

**Module: 1: Minimization and Transformation of Sequential Machines::** The Finite State Model – Capabilities and limitations of FSM – State equivalence and machine minimization – Simplification of incompletely specified machines. Fundamental mode model – Flow table – State reduction – Minimal closed covers – Races, Cycles and Hazards. **[10 hours] [Knowledge]**

**Module: 2: Advanced Digital Design and SM Charts::** Digital Design Using ROMs, PALs and PLAs, BCD Adder, 32 – bit adder, State graphs for control circuits, shift and add multiplier, Binary divider. - State machine charts, Derivation of SM Charts, Realization of SM Chart, Implementation of Binary Multiplier.

# [10 hours] [Comprehension ]

**Module 3:** Fault Modeling: Logic Fault model – Fault detection & Redundancy Fault equivalence and fault location – Fault dominance – Single stuck at fault model – Multiple stuck at fault models –Bridging fault model. [11 hours] [Comprehension]

Module 4: Fault Diagnosis: Fault diagnosis of combinational circuits by conventional methods – Path sensitization techniques, Test algorithms – D algorithm, PODEM, Random testing, Transition count testing, Signature analysis and test bridging faults.

[11 hours] [Comprehens]

# SKILL SETS TO BE DEVLOPED:

- 1. An attitude of enquiry.

- 2. Confidence and ability to tackle new problems.

- 3. Ability to interpret events and results.

- 4. Write reports.

- 5. The ability to follow standard /Legal procedures.

- 6. An awareness of the Professional Ethics.

**DELIVERY PROCEDURE (PEDAGOGY):** Lectures will be conducted with aid of Microsoft Teams. Assignments based on course contents will be given to the students at the end of each unit/topic and will be evaluated at regular interval.

**SELF-LEARNING TOPICS:** Kohavi algorithm, Test Pattern Generation, D – algorithm, PODEM Testable PLA design.

BLENDED LEARNING USING VIDEOS: PAL and PLA.

FLIPPED CLASS ROOM TOPIC: State machine reduction technique

PARTICIPATIVE LEARNING: How Optimization Algorithms are applicable for state reduction

#### **REFERENCE MATERIALS: Textbooks, reference books, any other resources, like webpages.**

#### (i) Text Books:

#### **Text Books:**

- 4. N. N. Biswas, *"Logic Design Theory"*, PHI, 2009. ISBN:9780135243985, 013524398X the University of Michigan- Prentice Hall

- 5. Zvi Kohavi, "Switching and Finite Automata Theory", TMH, 2nd Edition, 2005.

- 6. Norman Balabanian, Bradley Carlson, "Digital Logic Design Principles" Wiley Student Edition, 2007

# (ii) Reference book:

- 4. M. Abramovici, Melnin Breuer, Arthur Friedman, "*Digital System Testing and Testable Design*", Jaico Publications, Reprint Edition, 2008.

- 5. Charles H. Roth Jr., "Fundamentals of Logic Design", Cengage learning, 6th Edition, 2004.

- 6. Frederick. J. Hill & Peterson, "Computer Aided Logic Design", Wiley 4th Edition, 1993.

(iii) Class Notes:

(iv) E-content:

- 10. State Minimization in synchronous sequential circuits YouTube

- 11. Sequence detector 1100 || sequence detector 1101 overlapping mealy FSM YouTube

- 12. Ebook1: Find PDF Logic Design Theory (colorado.edu)

- 13. Ebook2: Digital Systems Design | Download book (freebookcentre.net)

- 14. Nptel Digital System Design Course (nptel.ac.in)

- 15. NPTEL :: Electrical Engineering NOC:Digital System Design

- 16. <u>https://www.researchgate.net/publication/348235247\_Advanced\_Digital\_System\_Design\_-</u> <u>A\_Practical\_Guide\_to\_Verilog\_Based\_FPGA\_and\_ASIC\_Implementation/link/5ff4764d92851c13feefa0</u> <u>d2/download</u>

- 17. <u>https://www.researchgate.net/publication/3897013\_Fault\_Equivalence\_Identification\_Using\_Redundanc</u> <u>y\_Information\_and\_Static\_and\_Dynamic\_Extraction</u>

- 18. http://www.pld.ttu.ee/diagnostika/theory/fault.html

# **GUIDELINES TO STUDENTS:**

Students have to attend classes regularly and follow the session very carefully. Here in handout we mentioned pre requisitions, go through the topics once. The students are directed to maintain separate note book to write important discussions/key points during the lecture

PRESIDENCY UNIVERSITY LIBRARY LINK: https://presiuniv.knimbus.com/user#/home

# **COURSE SCHEDULE:**

| Sl. No. | ACTIVITY                     | STARTING<br>DATE | CONCLUDING<br>DATE | TOTAL NUMBER<br>OF PERIODS |

|---------|------------------------------|------------------|--------------------|----------------------------|

| 1.      | Over View of the course      |                  |                    | 01                         |

| 2.      | Module : 01                  |                  |                    | 12                         |

| 3.      | Module 01 revision           |                  |                    | 1                          |

| 4.      | Assignment 1                 |                  |                    |                            |

| 5.      | Module : 02                  |                  |                    | 13                         |

| 6.      | Module 02 revision           |                  |                    | 1                          |

| 7.      | Mid Term Examination         |                  |                    | NA                         |

| 8.      | Mid Term Paper Discussion    |                  |                    | 03                         |

| 9.      | Module:03                    |                  |                    | 10                         |

| 8       | Group Discussion /Case Study |                  |                    |                            |

| 9       | End Term Examination         |                  |                    | NA                         |

|         | 1                            |                  | TOTAL              | 41                         |

# SCHEDULE OF INSTRUCTION

| Sl.<br>No | Session No /<br>Date* | Lesson Title               | Topics                                                                                                             | CO<br>No | Delivery Mode                | Reference |

|-----------|-----------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------|----------|------------------------------|-----------|

| 1.        |                       | Overview and integration   | Introduction to Advanced digital design concepts and explanation of how they are related with Digital Electronics. | -NA-     | Online<br>Microsoft<br>Teams |           |

| 2.        |                       |                            | Characteristics of Digital Systems.                                                                                | 1        |                              | CN,<br>R1 |

| 3.        |                       | The Finite State<br>Model. | Capabilities and limitations of FSM                                                                                | 1        |                              | CN,<br>R1 |

| 4.        |                       |                            | State equivalence and machine minimization                                                                         | 1        |                              | CN,<br>R1 |

| 5.        |                       |                            | Simplification of incompletely specified machines                                                                  | 1        |                              | CN, R1    |

| 6.        |                       | FSM Design                 | Fundamental mode model                                                                                             | 1        |                              | CN, T1    |

| 7.        |                       |                            | Sequence detector FSM (Mealy overlapping and Non-overlapping)                                                      | 2        |                              | CN, T1    |

| 8.        |                       |                            | Sequence detector FSM (Moore non-overlapping and overlapping)                                                      | 2        |                              |           |

| 9.        |                       |                            | Flow table , State reduction – Minimal closed covers                                                               | 2        |                              |           |

| 10.       |                       |                            | Races, Cycles and Hazards.                                                                                         | 2        | -0                           | T1 R1 CN  |

| 11. | Advanced Digital<br>Design | Digital Design Using ROMs PALs and PLAs                                                                    | 4               | T1 R1 CN                    |

|-----|----------------------------|------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------|

| 12. |                            | BCD Adder, 32 – bit adder                                                                                  | 4               | T1 R1 CN                    |

| 13. | SM Charts:                 | State graphs for control circuits                                                                          | 4               | T1 R1 CN                    |

| 14. |                            | shift and add multiplier                                                                                   | 4               | T1 R1 CN                    |

| 15. |                            | Binary divider                                                                                             | 4               | T1 R1 CN                    |

| 16. |                            | State machine charts                                                                                       |                 | T1 R1                       |

| 17. |                            | Derivation of SM Charts                                                                                    | 4               | CN<br>T1 R1<br>CN           |

| 18. |                            | Realization of SM Chart                                                                                    | 4               | T1 R1<br>CN                 |

| 19. |                            | Implementation of Binary<br>Multiplier                                                                     | 4               | T1 R1<br>CN                 |

| 20. |                            | Mid Sem Exam Review                                                                                        | 3               | T1 R1                       |

| 21. |                            | Mid Sem Exam Discussion                                                                                    | 4               | CN<br>T1 R1<br>CN           |

| 22. | Logic Fault model          | FAULT                                                                                                      |                 | CN                          |

| 23. |                            | Fault dominance                                                                                            | 4               | T1 R1 CN                    |

| 24. |                            | Single stuck at fault model                                                                                |                 |                             |

| 25. |                            | Multiple stuck at fault models                                                                             |                 |                             |

| 26. |                            | Bridging fault model                                                                                       |                 |                             |

| 27. |                            | Course Project Progress Review                                                                             |                 |                             |

| 28. |                            | Course Project Progress Review                                                                             |                 |                             |

| 29. | Fault Modelling            | Fault Modeling & Test Pattern<br>Generation: Logic Fault model                                             | 4               | T1 R1 CN                    |

| 30. |                            | Fault detection & Redundancy<br>Fault equivalence and fault<br>location                                    | 4               | T1 R1 CN                    |

| 31. |                            | Fault dominance – Single stuck at<br>fault model – Multiple stuck at<br>fault models–Bridging fault model. |                 |                             |

|     |                            | Completion of Module 3                                                                                     |                 |                             |

| 32. | Fault diagnosis            | Fault diagnosis of combinational<br>circuits by conventional methods                                       | 4               | CN                          |

| 33. |                            | Path sensitization techniques.                                                                             | 4               | CN                          |

| 34. |                            | Test algorithms                                                                                            | 4               | CN                          |

| 35. |                            | Examples for test patterns generation                                                                      |                 |                             |

| 36. |                            | Examples Continued                                                                                         |                 |                             |

| 37. |                            | PODEM, Random testing                                                                                      |                 |                             |

| 38. |                            | Transition count testing                                                                                   |                 |                             |

| 39. |                            | Signature analysis and test bridging faults.                                                               | 0               |                             |

| 40. |                            |                                                                                                            | ALUNE ENCY UNIT |                             |

| I   |                            |                                                                                                            | REGISTRAR       | Page <b>8</b> of <b>1</b> 3 |

|     | Completion of Module 4 |                                   |  |  |  |

|-----|------------------------|-----------------------------------|--|--|--|

| 41. | 24/03/2021             | Project Submission and Evaluation |  |  |  |

| 42. | 26/03/2021             | End Term Exam Review              |  |  |  |

\* These dates are only indicative - applicable to one section handled by subject IC. Dates will vary from section to section.

# **ASSESSMENT SCHEDULE:**

**Topics relevant to "Skill development":** Machine Minimization For developing **Skill development**" through **Participative Learning techniques**. This is attained through the Project as mentioned in the assessment component

| SI.<br>No | Assessment<br>type                                                                                                                                                                                                                                   | Contents                                                                                                                                                                                                                                              | CO. NO        | Duration<br>In<br>Minutes | Marks    | Weightage | Venue,<br>DATE<br>&TIME                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------|----------|-----------|------------------------------------------------------------|

| 1.        | Mid Term                                                                                                                                                                                                                                             | Module<br>1,2                                                                                                                                                                                                                                         | C01,C02       | 90 min                    | 60       | 30%       |                                                            |

| 2.        | End term<br>Examination                                                                                                                                                                                                                              | Module<br>1,2,3                                                                                                                                                                                                                                       | CO1,CO2,CO3   | 180 min                   | 100      | 50%       |                                                            |

| 3.        | Mini Project                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | C01,C02,C03   | NA                        | 20       | 10%       |                                                            |

| 4.        | Assignment                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                       | CO1, CO2, CO3 | NA                        | 10       | 5%        |                                                            |

| 5.        | Assignment-<br>Review of<br>digital / e-<br>resources from<br>Pres. Univ.<br>link given in<br>the References<br>Section -<br>(Mandatory to<br>submit<br>screenshot<br>accessing<br>digital<br>resource.<br>Otherwise it<br>will not be<br>evaluated) | https://doi.<br>org/10.101<br>6/j.procs.2<br>021.01.17<br>1<br>https://doi.<br>org/10.101<br>6/j.micpro.<br>2020.1037<br>82<br>https://doi.<br>org/10.101<br>6/j.micpro.<br>2020.1037<br>25<br>https://doi.<br>org/10.101<br>6/j.neunet.<br>2019.09.0 | CO1,CO2,CO3   | NA                        | 10       | 5%        | Will be<br>announced<br>one week<br>prior to<br>submission |

|           |                                                                                                                                                                                                                                                      | · · ·                                                                                                                                                                                                                                                 | 1             | 1                         | REGISTRA | SEC (C)   | Page <b>9</b> of <b>13</b>                                 |

| $\underline{2\underline{4}}$ . |  |

|--------------------------------|--|

|                                |  |

|                                |  |

**COURSE CLEARANCE CRITERIA**: A minimum of 75% attendance is required to attend the end term exam. Makeup policy will be only as per academic regulation. There will be no make-up for ASSIGNMENT and QUIZ

|    | Method of Assessment                                                                                                                                    |                                    |                                  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------|

|    | for Courses with Credit Structure $(L - T - 0)$ or $(L - 0 - 0)$                                                                                        |                                    |                                  |

|    | Components of Continuous<br>Assessments                                                                                                                 | Weightage<br>(% of Total<br>Marks) | Duration<br>of<br>Assessm<br>ent |

| 1. | Mid Term                                                                                                                                                | 30%                                | 1.5 hour                         |

| 2. | This Component of continuous assessment shall consist of at least TWO (02) of the following:<br>(1) Group Discussion /Case Study<br>(2) Assignment/Quiz |                                    |                                  |

|    |                                                                                                                                                         | 20%                                | NA                               |

| 3. | End Term Final Examinations                                                                                                                             | 50%                                | 3 hours                          |

|    | Total                                                                                                                                                   | 100%                               |                                  |

# **MAKEUP POLICY:**

If the student misses an evaluation component, he/she may be granted a make-up. In case of an absence that is foreseen, make-up request should be personally made to the Instructor-in-Charge, well ahead of the scheduled evaluation component. Reasons for unanticipated absence that qualify a student to apply for make-up include medical emergencies or personal exigencies. In such an event, the student should contact the Instructor-in-Charge as soon as practically possible.

**CONTACT TIMINGS IN THE CHAMBER FOR ANY DISCUSSIONS:** It will be announced in the class. Interested students may meet the Instructor In-charge during the Chamber Consultation Hour to clear doubts.

# SAMPLE THOUGHT PROVOKING QUESTIONS:

| SL<br>NO | QUESTION                                                                   | MARKS     | CO.<br>NO. | BLOOM'S<br>LEVEL            |

|----------|----------------------------------------------------------------------------|-----------|------------|-----------------------------|

| 1.       | A digital system is to be designed in which the month of the year is given | 6         | CO1        | L2                          |

|          | as input in four bit form. The month January is represented as '0000',     | anne      | YUN        |                             |

|          | c.                                                                         | REGISTRAR | gistrar    | Page <b>10</b> of <b>13</b> |

|    | February '0001' and so on. The output of the system should be '1' corresponding to the input of the month containing 31 days or otherwise it is '0'. Consider the excess numbers in the input beyond '1011' as don't care conditions for system of four variables (A, B, C, D). Design and implement the simplified logic using NAND Gates. |    |                     |    |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------|----|

| 2. | Explain and Sketch FSM for Keypad scanner and Encoder.                                                                                                                                                                                                                                                                                      | 4  | CO2                 | L3 |

| 3. | Discuss the internal and external design challenges faced by an design<br>engineer while implementing a sequential design for a traffic system.                                                                                                                                                                                             | 6  | CO1                 | L2 |

| 4. | Design an 4 bit ALU in HDL environment. Integrate the functionalities and verify it.                                                                                                                                                                                                                                                        | 12 | CO1,<br>CO2,<br>CO4 | L4 |

# Target set for course Outcome attainment:

| Sl.<br>No | CO.<br>No. | Course Outcomes                                                | Target set for<br>attainment in<br>percentage |

|-----------|------------|----------------------------------------------------------------|-----------------------------------------------|

| 1         | CO1        | Summarize the minimization theories of Sequential Machines     | 50%                                           |

| 2         | CO2        | Discover the sequential circuit using programmable devices.    | 40%                                           |

| 3         | CO3        | Practice the techniques for fault modeling of digital systems. | 50%                                           |

|           | CO4        | Illustrate the various Fault diagnosis algorithm               | 50%                                           |

Signature of the course Instructor:

This course has been duly verified Approved by the D.A.C.

Signature of the Chairperson D.A.C.

Course Completion Remarks & Self-Assessment. [This has to be filled after the completion of the course]

[Please mention about the course coverage details w.r.t. the schedule prepared and implemented. Any specific suggestions to incorporate in the course content. Any Innovative practices followed and its experience. Any specific suggestions from the students about the content, Delivery, Evaluation etc.]

| Sl.no. | Activity | Scheduled Completion Date | Actual Completion Date | Remarks |                        |

|--------|----------|---------------------------|------------------------|---------|------------------------|

|        |          |                           | anne                   |         |                        |

|        |          |                           | REGISTRAR              | Page    | <b>11</b> of <b>13</b> |

|   | As listed in the course Schedule |  |  |

|---|----------------------------------|--|--|

| 1 | Midterm Examination              |  |  |

| 3 | End term Examination             |  |  |

| 4 | Mini Project / Assignment        |  |  |

Any specific suggestion/Observations on content/coverage/pedagogical methods used etc.:

Course Outcome Attainment:

| Sl.no | C.O. | Course Outcomes                 | Target set | for | Actual C.O.   | Remarks    | on  |

|-------|------|---------------------------------|------------|-----|---------------|------------|-----|

|       | No.  |                                 | attainment | in  | Attainment    | attainment |     |

|       |      |                                 | percentage |     |               | &Measures  | to  |

|       |      |                                 |            |     | In Percentage | enhance    | the |

|       |      |                                 |            |     |               | attainment |     |

|       |      |                                 |            |     |               |            |     |

| 01    | CO1  | Summarize the minimization      | 50%        |     |               |            |     |

|       |      | theories of Sequential          |            |     |               |            |     |

|       |      | Machines                        |            |     |               |            |     |

|       |      |                                 |            |     |               |            |     |

| 02    | CO2  | Discover the sequential circuit | 40%        |     |               |            |     |

|       |      | using programmable devices.     |            |     |               |            |     |

| 0.2   | 0.00 |                                 | 500/       |     |               |            |     |

| 03    | CO3  | Practice the techniques for     | 50%        |     |               |            |     |

|       |      | fault modeling of digital       |            |     |               |            |     |

|       |      | systems.                        |            |     |               |            |     |

| 0.1   | 004  |                                 | 500/       |     |               |            |     |

| 04    | CO4  | Illustrate the various Fault    | 50%        |     |               |            |     |

|       |      | diagnosis algorithm             |            |     |               |            |     |

|       |      |                                 |            |     |               |            |     |

Name and signature of the Faculty member:

D.A.C. observation and approval:

# **BLOOM'S TAXONOMY**

Learning Outcomes Verbs at Each Bloom Taxonomy Level to be used for writing the course Outcomes.

| Cognitive Level | Illustrative Verbs                                                                                                                                                                                                                                                                                                 | Definitions                                                                                               |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Knowledge       | arrange, define, describe, duplicate, identify, label,<br>list, match, memorize, name, order, outline,<br>recognize, relate, recall, repeat, reproduce, select,<br>state                                                                                                                                           | remembering previously learned information                                                                |

| Comprehension   | classify, convert, defend, discuss, distinguish,<br>estimate, explain, express, extend, generalize, give<br>example(s), identify, indicate, infer, locate,<br>paraphrase, predict, recognize, rewrite, report,<br>restate, review, select, summarize, translate                                                    | grasping the meaning of information                                                                       |

| Application     | apply, change, choose, compute, demonstrate,<br>discover, dramatize, employ, illustrate, interpret,<br>manipulate, modify, operate, practice, predict,<br>prepare, produce, relate schedule, show, sketch,<br>solve, use write                                                                                     | applying knowledge to actual situations                                                                   |

| Analysis        | analyze, appraise, breakdown, calculate, categorize,<br>classify, compare, contrast, criticize, derive,<br>diagram, differentiate, discriminate, distinguish,<br>examine, experiment, identify, illustrate, infer,<br>interpret, model, outline, point out, question, relate,<br>select, separate, subdivide, test | breaking down objects or ideas into<br>simpler parts and seeing how the parts<br>relate and are organized |

| Synthesis       | arrange, assemble, categorize, collect, combine,<br>comply, compose, construct, create, design,<br>develop, devise, explain, formulate, generate, plan,<br>prepare, propose, rearrange, reconstruct, relate,<br>reorganize, revise, rewrite, set up, summarize,<br>synthesize, tell, write                         | rearranging component ideas into a new whole                                                              |

| Evaluation      | appraise, argue, assess, attach, choose, compare,<br>conclude, contrast, defend, describe, discriminate,<br>estimate, evaluate, explain, judge, justify, interpret,<br>relate, predict, rate, select, summarize, support,<br>value                                                                                 | making judgments based on internal<br>evidence or external criteria                                       |

#### PRESIDENCY NIVERS

Private University Estd. in Karnataka State by

# SCHOOL of ENGINEERING

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

| er: M.Tech.,(ESV) Section: |

|----------------------------|

| l System Design.           |

|                            |

| nt                         |

| rning                      |

| i <b>G</b> .               |

| G                          |

| xed to present on any      |

| ault Models                |

|                            |

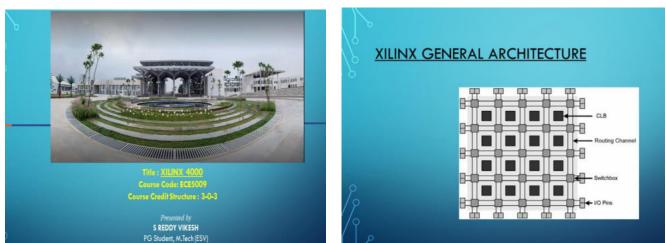

# Details of the students involved in the activity:

| S.No | Name of the Student | Roll Number  |

|------|---------------------|--------------|

| 1    | CHARAGUDI DHANYA    | 20222ESV0001 |

| 2    | SETTY REDDY VIGNESH | 20222ESV0002 |

# Date of presentation: 11.4.23 & 12.4.23

A fault model identifies targets for testing. Drastically reduces the number of faults. Makes analysis possible. Effectiveness measurable by experiments.

City Office: University House, 8/1, King Street, Richmond Town, Bengaluru - 560025 Campus: Presidency University, Itgalpur, Rajankunte, Bengaluru - 560064 Phone: + 80 4925 5533 / 5599 Email ID: info@presidencyuniversity.in

www.presidencyuniversity.in

# **Remarks:**

- By participating in this presentation, students were learned about the Fault Models Descriptions.

- This learning will **Develop their Skills** in Identify the fault in any machines •

Signature of Instructor:

Signature of Instructor In-Charge :

**HOD - ECE**

City Office: University House, 8/1, King Street, Richmond Town, Bengaluru - 560025 Campus: Presidency University, Itgalpur, Rajankunte, Bengaluru - 560064 Phone: + 80 4925 5533 / 5599 Email ID: info@presidencyuniversity.in www.presidencyuniversity.in

Presidency University Act, 2013 of the Karnataka Act No. 41 of 2013 | Established under Section 2(f) of UGC Act, 1956 Approved by AICTE, New Delhi

Itgalpur, Rajankunte, Yelahanka, Bengaluru – 560064

| Course Code:<br>ECE5008         | <b>Course Title:</b> Software for Embed<br><b>Type of Course:</b> Program Core | lded System          | L-P-C 3                        | 0           | 3            |

|---------------------------------|--------------------------------------------------------------------------------|----------------------|--------------------------------|-------------|--------------|

| ECESUUO                         | Theory                                                                         |                      |                                | 0           | 3            |

| Version No.                     | 1.0                                                                            |                      |                                | 1           |              |

| Course Pre-                     | Before attempting this course the                                              |                      | •                              | U           | Digital      |

| requisites                      |                                                                                | -                    | g of Micropro                  |             | and/or       |

|                                 | Microcontrollers, Assembly Langu                                               |                      |                                |             |              |

|                                 | Microcontrollers, Prior C Program                                              | mming knowledg       | ge (would be an a              | dded adv    | antage       |

|                                 | but not compulsory).                                                           |                      |                                |             |              |

|                                 |                                                                                |                      |                                |             |              |

| Anti-requisites                 | NIL                                                                            |                      |                                |             |              |

| Course                          | This course focuses on the develop                                             |                      |                                |             |              |

| Description                     | Students will be exposed to var<br>embedded products.                          | lous techniques      | for writing effi               | cient coc   | les for      |

|                                 | The course will begin by giving an                                             | overview of cont     | rolling hardware               | systems u   | ising C      |

|                                 | programming language. In the nex                                               | t level use of Inte  | grated Developme               | ent Enviro  | onment       |

|                                 | (IDE) tools will be undertaken fo<br>design. Installation of software t        | 0                    | 00                             |             |              |

|                                 | hardware kits etc. will be the key                                             |                      |                                |             |              |

|                                 | independent software developmen                                                | t students will be   | trained in compi               | lation and  | d make       |

|                                 | process by using various open-so                                               |                      |                                |             |              |

|                                 | GNU, Git version control, Linux,<br>memory management, device driv             |                      |                                | • •         |              |

|                                 | and interrupt systems, interfacing                                             |                      |                                |             |              |

|                                 | embedded systems will make stude                                               |                      |                                |             | 8            |

|                                 |                                                                                |                      |                                |             |              |

| Course                          | The objective of the course is to                                              | o familiarize the    | e learners with t              | he softwa   | are for      |

| Objective                       | embedded systems and attain <u>SKILI</u>                                       | <u>. DEVELOPMENT</u> | through <mark>PARTICPA</mark>  | TIVE LEA    | <u>rning</u> |

| Course                          | On successful completion of this co                                            | ourse the student    | s shall be able to:            |             |              |

| Outcomes                        | 1. Summarize the concepts to c                                                 | levelon software f   | or real time embed             | lded syste  | ms           |

|                                 | 2. Write efficient programs wit                                                | <u> </u>             |                                | laca system |              |

|                                 | 3. Demonstrate various progra                                                  |                      | -                              | npilers an  | nd tools     |

|                                 | for embedded software deve                                                     | lopment.             |                                |             |              |

|                                 | 4. Explain various concepts o                                                  |                      |                                |             |              |

|                                 | interrupt systems, interfacing                                                 | ng of devices, co    | ommunications an               | d networl   | king in      |

|                                 | embedded systems.                                                              |                      |                                |             |              |

| Course                          |                                                                                |                      |                                |             |              |

| Content:                        |                                                                                |                      |                                |             |              |

|                                 |                                                                                |                      |                                |             |              |

| Module 1                        | Introduction to Embedded<br>Systems Software Development                       | Quiz                 | Memory Recall<br>based Quizzes | 7 ses       | ssion        |

| Topics:                         |                                                                                |                      |                                |             |              |

| *                               | bedded Systems and Application A                                               | reas, Fundament      | als of Software                | Engineeri   | ng and       |

| Review of Eml                   | bedded Systems and Application A<br>rocesses, Embedded Software - Safet        |                      |                                | -           | -            |

| Review of Eml<br>Development Pr |                                                                                | y, Security and (    | Quality, Introducti            | -           | -            |

REGISTRAR

Registra

| Module 2                                                                                                                                                                                                         | C-Programming for Embedded<br>Systems           | Assignment /<br>Quiz | Programming               | 8 session          |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------|---------------------------|--------------------|--|--|

| Topics:<br>Review of modeling languages for Embedded Software development, C-Programming Review, Programming                                                                                                     |                                                 |                      |                           |                    |  |  |

| ARM Controller                                                                                                                                                                                                   | rs using C – Conditional Statemen               | its, Loop Statem     | ents, debugging, s        | single stepping,   |  |  |

| breakpoints, poin                                                                                                                                                                                                | ters and data structures, variables, nur        | nbers and parame     | ter passing.              |                    |  |  |

|                                                                                                                                                                                                                  |                                                 |                      |                           |                    |  |  |

| Module 3                                                                                                                                                                                                         | Memory Management and<br>Device Driver Concepts | Assignment           | Analysis and Verification | 17 session         |  |  |

| Topics:<br>Introduction to N                                                                                                                                                                                     | Memory Organization, Memory Archi               | tectures, Memory     | v Segments, Data M        | femory, Special    |  |  |

| Keywords (Cons                                                                                                                                                                                                   | t, Extern & Static), The Stack, The Hea         | ap, Code Memory      | , Practice on Memo        | ry Manipulation    |  |  |

| Software, Incorp                                                                                                                                                                                                 | orate Memory Manipulation Software              | e into the build sy  | stem and Evaluation       | on of some Test    |  |  |

| Functions. Linux                                                                                                                                                                                                 | - Scripting and Configuration, Kerne            | el Building, Build   | ing Libraries and U       | Itilities, Generic |  |  |

| Device Driver De                                                                                                                                                                                                 | evelopment Concepts, Linux Device D             | Drivers.             |                           |                    |  |  |

| Project Work/Assignment:                                                                                                                                                                                         |                                                 |                      |                           |                    |  |  |

|                                                                                                                                                                                                                  |                                                 |                      |                           |                    |  |  |

| 1.Case Studies: At the end of the course students will be given 'real-world' application-based circuits like traffic light controller, LCD display, DC motor etc. as a case study. Students will be submitting a |                                                 |                      |                           |                    |  |  |

1. Case Studies: At the end of the course students will be given 'real-world' application-based circuits like traffic light controller, LCD display, DC motor etc. as a case study. Students will be submitting a report which will include Circuit Diagrams, Design, Working Mechanism and Results etc. in appropriate format.

2. Book/Article review: At the end of each module a book reference or an article topic will be given to an individual or a group of students. They need to refer to the library resources and write a report on their understanding about the assigned article in an appropriate format. <u>Presidency University Library Link</u>.

**3.** Presentation: There will be a group presentation, where the students will be given a topic. They will have to explain/demonstrate the working and discuss the applications for the same.

4. Project Assignment: (Don't be specific)

# Assignment 1:

Recently there have been lot of controversies over use of Electronic Voting Machine (EVM) Systems in elections. You have been asked to design an "EVM System" to be used in elections. The system will have additional facility to webcast the voting process live to a central station using Wi-Fi/3G/4G connection by using a high-resolution camera and/or tablet (as of now avoid VVPAT facility). Draw a FSM diagram considering various states, inputs and Outputs.

# Assignment 2:

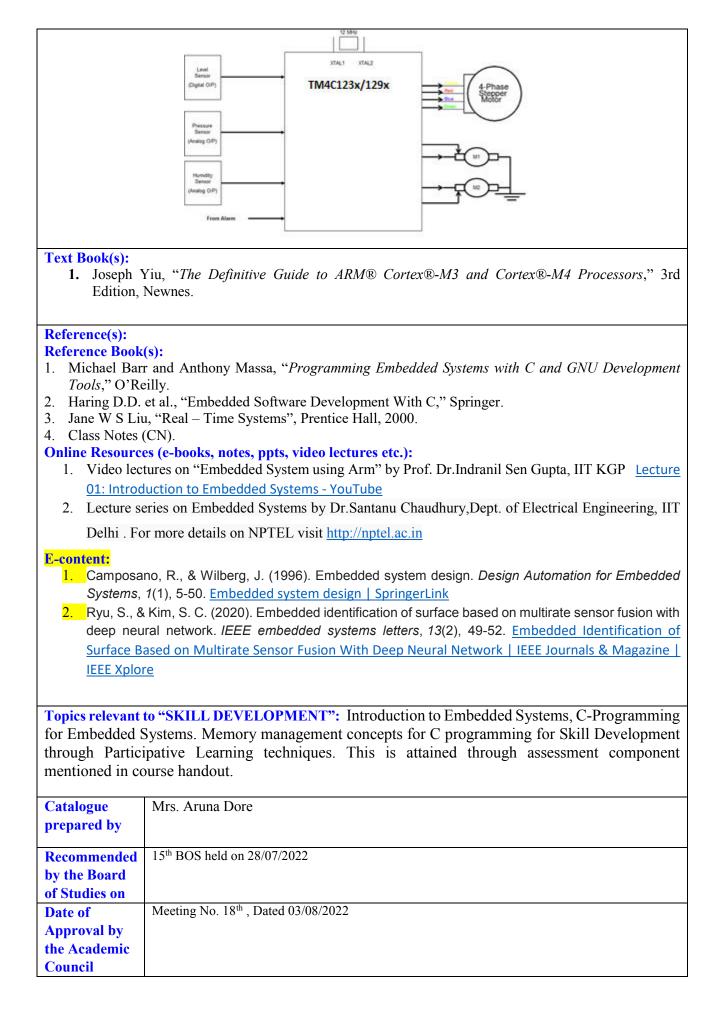

Consider the figure shown below showing the layout of an Embedded System to be designed using the TM4C123x/129x microcontroller. Write a device driver for the individual modules shown such as for stepper motor control, dc motor control, timer and sensing inputs both digital as well as analog.

anne REGISTRAR

# (Established under the Presidency University Act, 2013 of the Karnataka Act 41 of 2013)

# ACA-2[2021] COURSE HAND OUT

| SCHOOL: SOE             | DEPT.: ECE                                             | DATE OF ISSUE: 27/08/2022 |  |

|-------------------------|--------------------------------------------------------|---------------------------|--|

| NAME OF THE PROGRAM     | <b>THE PROGRAM</b> : M. Tech. Embedded System and VLSI |                           |  |

| P.R.C. APPROVAL REF.    | : PU/AC-18.4/ECE15/ESV/2022-24                         |                           |  |

| SEMESTER/YEAR           | :1                                                     |                           |  |

| COURSE TITLE & CODE     | : Software for Embedded Systems (ECE 5009)             |                           |  |

| COURSE CREDIT STRUCTURE | : 3-0-0-3                                              |                           |  |

| CONTACT HOURS           | : 45                                                   |                           |  |

| COURSE INSTRUCTOR       | : Dr. Joseph Antho                                     | ny Pratap                 |  |

**PROGRAM OUTCOMES** : Bolded outcomes are met by this course. Others are not met.

Graduates of the M. Tech. Program in Embedded System and VLSI will have the following abilities:

PO1. An ability to apply knowledge of mathematics, science and engineering in practice.

PO2. An ability to identify, critically analyze, formulate and solve engineering problems with comprehensive knowledge in the area of specialization.

PO3. An ability to select modern engineering tools and techniques and use them with dexterity.

PO4. An ability to design a system and process to meet desired needs within realistic constraints such as health, safety, security and manufacturability.

PO5. An ability to contribute by research and innovation to solve engineering problems.

PO6. An ability to devise and conduct experiments, interpret data and provide well-informed conclusions.

PO7. An ability to understand the impact of engineering solutions in a contemporary, global, economic, environmental, and societal context for sustainable development.

PO8. An ability to function professionally with ethical responsibility as an individual as well as in multidisciplinary teams with a positive attitude.

PO9. An ability to communicate effectively.

PO10. An ability to appreciate the importance of goal setting and to recognize the need for life-long reflective learning.

**COURSE PREREQUISITES:**

Before attempting this course the student should have prior knowledge of Digital Logic and Operators, Some understanding of Microprocessors and/or Microcontrollers, Assembly Language Programming of any Microprocessors and/or Microcontrollers, Prior C Programming knowledge (would be an added advantage but not compulsory).

# **COURSE DESCRIPTION:**

This course focuses on the development of software for real-world embedded systems. Students will be exposed to various techniques for writing efficient codes for embedded products.

The course will begin by giving an overview of controlling hardware systems using C programming language. In the next level use of Integrated Development Environment (IDE) tools will be undertaken for building and managing efficient programs and design. Installation of software tools as well as virtual machines, controlling of hardware kits etc. will be the key elements. To augment the learning process for independent software development students will be trained in compilation and make process by using various open-source compilers and tools such as GNU toolchain GNU, Git version control, Linux, Virtual Machines etc. Additionally, concepts like memory management, device driver development, compilers and debuggers, timers and interrupt systems, interfacing of devices, communications and networking in embedded systems will make students ready for industry.

# **COURSE OBJECTIVE**

The objective of the course is to familiarize the learners with the software for embedded systems and attain SKILL DEVELOPMENT through PARTICPATIVE LEARNING.

# **COURSE OUTCOMES:**

#### On successful completion of the course the students shall be able to

- 5. Summarize the concepts to develop software for real time embedded systems.

- 6. Write efficient programs with IDE tools for embedded systems.

- 7. Demonstrate various programming steps using open-source compilers and tools for embedded software development.

- 8. Explain various concepts of memory management, device drivers, timers and interrupt systems, interfacing of devices, communications and networking in embedded systems.

# MAPPING OF C.O. WITH P.O.

# [H-HIGH, M-MODERATE, L-LOW]

| CO. NO. | PO1 | PO2 | PO3 | PO6 | PO8 | PO9 |

|---------|-----|-----|-----|-----|-----|-----|

|         |     |     |     |     |     |     |

|         |     |     |     |     |     |     |

| 1.      | L   | L   | L   |     |     | L   |

|         | _   | _   |     |     |     |     |

|         |     |     |     |     |     |     |

| 2.      | Μ   | Μ   | L   | L   | L   | L   |

| -       |     |     |     |     |     |     |

|         |     |     |     |     |     |     |

| 3.      | Μ   | Μ   | Μ   | Μ   | L   | L   |

|         |     |     |     |     |     |     |

|         |     |     |     |     |     |     |

| 4.      | Н   | Н   | Н   | Н   | Μ   | L   |

| -       |     |     |     |     |     |     |

|         |     |     |     |     |     |     |

# **COURSE CONTENT (SYLLABUS):**

**Module 1: Introduction to Embedded Systems Software Development:** Review of Embedded Systems and Application Areas, Fundamentals of Software Engineering and Development Processes, Embedded Software - Safety, Security and Quality, Introduction to Embedded Software Modeling, Context Diagrams, State Charts / Finite State Machines (FSMs),. (7 Hrs) [Blooms level selected: Comprehension Level]

**Module 2: C-Programming for Embedded Systems:** Review of modelling languages for Embedded Software development, C-Programming Review, Programming ARM Controllers using C – Conditional Statements, Loop Statements, debugging, single stepping, breakpoints, pointers and data structures, variables, numbers and parameter passing. (8 Hrs) [Blooms level selected: Application Level]

Module 3: Memory Management and Device Driver Concepts: Introduction to Memory Organization, Memory Architectures, Memory Segments, Data Memory, Special Keywords (Const, Extern & Static), The Stack, The Heap, Code Memory, Practice on Memory Manipulation Software, Incorporate Memory Manipulation Software into the build system and Evaluation of some Test Functions. Linux - Scripting and Configuration, Kernel Building, Building Libraries and Utilities, Generic Device Driver Development Concepts, Linux Device Drivers. (14 Hrs. Application Level) [Blooms level selected: Synthesis Level]

# **DELIVERY PROCEDURE (PEDAGOGY):**

Lectures will be conducted with the aid of online mode (MS Team), multi-media projector, blackboard and chalk.

- Assignments based on course contents will be given to the students at the end of each unit/topic and will be evaluated at regular intervals.

- Edhitch Quizzes will be conducted from time to time.

- Participative Learning: Seminar on important topics for development of quality and secure software for Embedded Systems will be arranged in a **flipped class group and/or individual space** mode.

- Project Based Learning: Students will develop a working software for any typical embedded application as partial fulfillment of the course in the form of a Software Development Project, either in a group or as an individual.

# **REFERENCE MATERIALS:** Textbooks, reference books, any other resources, like webpages.

# Text Book(s):

1. Joseph Yiu, "The Definitive Guide to ARM® Cortex®-M3 and Cortex®-M4 Processors," 3rd Edition, Newnes.

# **Reference Book(s):**

- 5. Michael Barr and Anthony Massa, "Programming Embedded Systems with C and GNU Development Tools," O'Reilly.

- 6. Haring D.D. et al., "Embedded Software Development With C," Springer.

- 7. Jane W S Liu, "Real Time Systems", Prentice Hall, 2000.

- 8. Class Notes (CN).

# Online Resources (e-books, notes, ppts, video lectures etc.):

1. Video lectures on "Embedded System using Arm" by Prof. Dr.Indranil Sen Gupta, IIT KGP \

Lecture 01: Introduction to Embedded Systems - YouTube

2. Lecture series on Embedded Systems by Dr.Santanu Chaudhury, Dept. of Electrical Engineering, IIT

Delhi . For more details on NPTEL visit http://nptel.ac.in

# **E-content:**

1.Camposano, R., & Wilberg, J. (1996). Embedded system design. Design Automation for Embedded

Systems, 1(1), 5-50. Embedded system design | SpringerLink

2. Ryu, S., & Kim, S. C. (2020). Embedded identification of surface based on multirate sensor fusion with deep neural network. IEEE embedded systems letters, 13(2), 49-52. Embedded Identification of Surface Based on Multirate Sensor Fusion With Deep Neural Network | IEEE Journals & Magazine | IEEE Xplore

Presidency University Library Link :- <u>https://presiuniv.knimbus.com/user#/home</u>

# **GUIDELINES TO STUDENTS:**

# Dear Students

Firstly I will ask you this – do NOT think of the course just as a course and count of credits to be met. This course deals with the software development practices which and Embedded Developer has to adopt. Therefore, start writing some basic level codes for accessing input and outputs ports and gradually move towards accessing on-chip as well as off-chip peripherals. I will be periodically sharing materials for various applications which you need to understand and develop your codes. **Initially, I will demonstrate working examples using simulators and on kits and later on you will do**. By the end of the semester you will all be able to implement your own mini projects on KEIL IDE for various embedded applications using ARM Cortex controller. **Together we will** create a healthy and fruitful learning environment.

COURSE SCHEDULE: (This is a macro level planning. Mention the unit wise expected starting and ending dates along with the tests/assignments/quiz and any other activities) [allot about 75% for delivery, about 10 to 12% for Evaluation Discussion, about 10 to 15% on integrating the learning Modules within the course and to the program]

| Sl. No. | ACTIVITY                                        | STARTING<br>DATE | CONCLUDING<br>DATE | TOTAL NO.<br>OF PERIODS |

|---------|-------------------------------------------------|------------------|--------------------|-------------------------|

| 1.      | Over View of the course and program integration |                  |                    | 1                       |

| 2.      | Module : 01                                     |                  |                    | 7                       |